Gerbang NOT merupakan gerbang di maan keluarannya akan selalu berlawanan dengan masukannya. Bila pada masukan diberikan tegangan, maka transistor akan jenuh dan keluaran bertegangan nol. Sedangkan bila pada masukannya diberi tegangan tertentu, maka transistor akan cut off, sehingga keluaran akan bertegangan tidak nol.

|

| Tabel 1.3 Tabel Kebenaran Logika NOT |

3. Rangkaian Simulasi[Kembali]

Pada percobaan pertama, digunakan empat flip-flop yang dirangkai pada modul De Lorenzo dengan konfigurasi tertentu. Flip-flop pertama memiliki pin S yang dihubungkan ke B6', pin J ke Q flip-flop kedua, pin K ke Q' flip-flop kedua, pin C ke output gerbang AND, pin R ke B0, dan pin Q ke H7. Flip-flop kedua memiliki pin S yang dihubungkan ke B5', pin J ke Q flip-flop ketiga, pin K ke Q' flip-flop ketiga, pin C ke output gerbang AND, pin R ke B0, dan pin Q ke H6. Pada flip-flop ketiga, pin S dihubungkan ke B4', pin J ke Q flip-flop keempat, pin K ke Q' flip-flop keempat, pin C ke output gerbang AND, pin R ke B0, dan pin Q ke H5. Sementara itu, pada flip-flop keempat, pin S dihubungkan ke B3', pin J ke B1, pin K ke B1', pin C ke output gerbang AND, pin R ke B0, dan pin Q ke H4. Gerbang AND pada rangkaian menerima input dari B2 dan sinyal clock (clk).

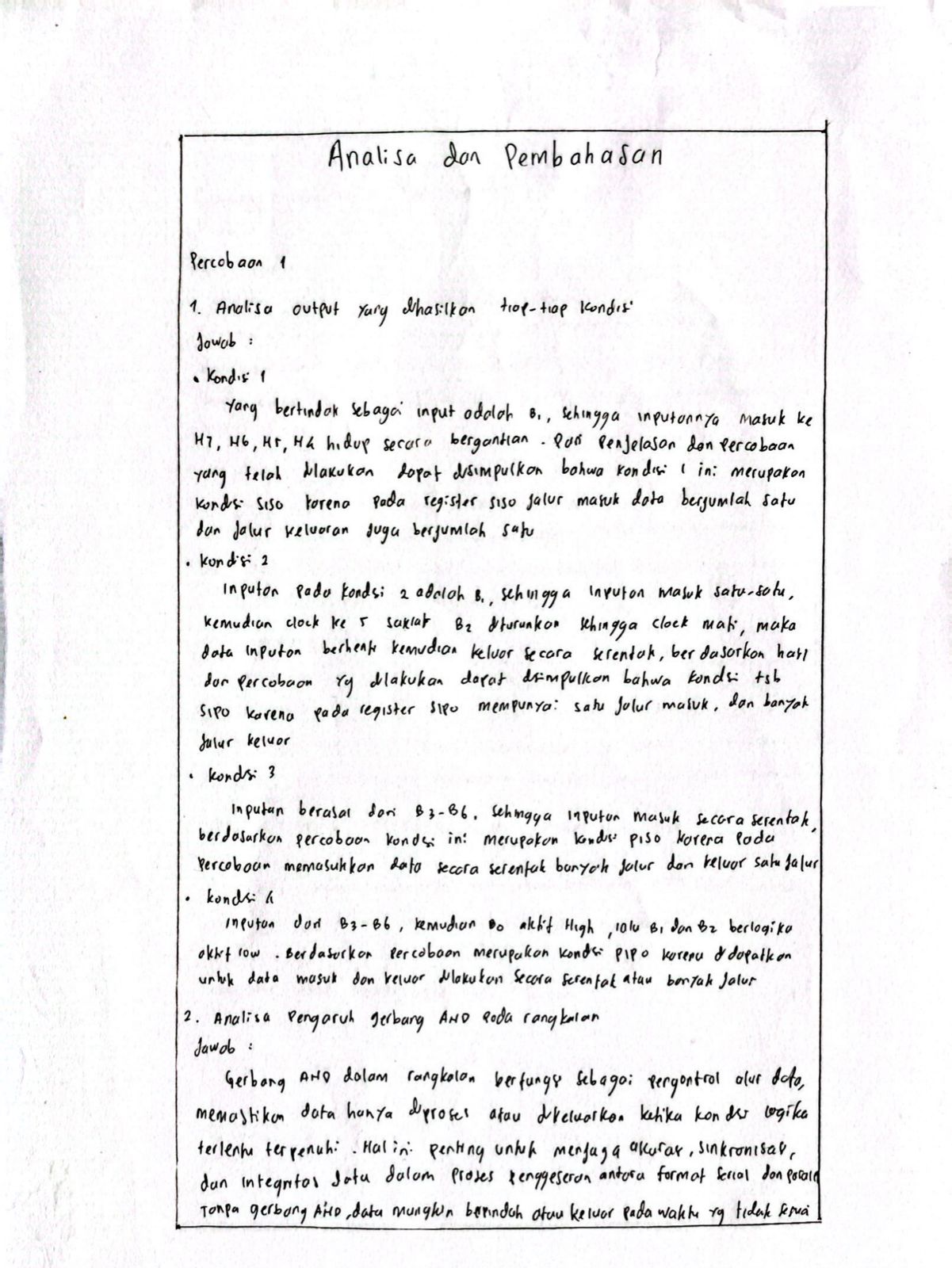

Percobaan dilakukan dengan memvariasikan input B0, B1, B2, B3, B4, B5, dan B6 untuk mengamati terjadinya pergeseran data dari kanan ke kiri. Berdasarkan hasil percobaan, jenis shift register yang digunakan dapat diklasifikasikan menjadi empat kondisi. Pada kondisi pertama, rangkaian bekerja sebagai SISO (Serial In Serial Out), di mana data masuk dan keluar satu per satu dengan pola pergeseran teratur. Kondisi kedua menunjukkan tipe SIPO (Serial In Parallel Out), di mana data masuk secara serial (bergantian) namun keluar secara serentak (parallel). Kondisi ketiga berupa PISO (Parallel In Serial Out), di mana data masuk serentak (parallel) tetapi keluar satu per satu (serial). Terakhir, kondisi keempat menunjukkan tipe PIPO (Parallel In Parallel Out), di mana data masuk dan keluar secara bersamaan (parallel).

Tidak ada komentar:

Posting Komentar